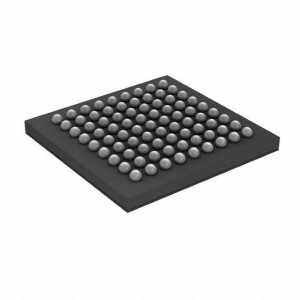

TMS320VC5509AZAY Лічбавыя сігнальныя працэсары і кантролеры – DSP, DSC з фіксаванай кропкай лічбавы сігнальны працэсар 179-NFBGA -40 да 85

♠ Апісанне прадукту

| Атрыбут прадукту | Значэнне атрыбута |

| Вытворца: | Texas Instruments |

| Катэгорыя прадукту: | Працэсары і кантролеры лічбавых сігналаў - DSP, DSC |

| RoHS: | Дэталі |

| прадукт: | DSP |

| серыя: | TMS320VC5509A |

| Стыль мантажу: | SMD/SMT |

| Пакет/чахол: | NFBGA-179 |

| Ядро: | C55x |

| Колькасць ядраў: | 1 ядро |

| Максімальная тактавая частата: | 200 МГц |

| Памяць інструкцый кэша L1: | - |

| Кэш-памяць дадзеных L1: | - |

| Памер памяці праграмы: | 64 кБ |

| Памер аператыўнай памяці для даных: | 256 кБ |

| Працоўная напруга харчавання: | 1,6 В |

| Мінімальная працоўная тэмпература: | - 40 С |

| Максімальная працоўная тэмпература: | + 85 С |

| Упакоўка: | паднос |

| Марка: | Texas Instruments |

| Тып інструкцыі: | Фіксаваная кропка |

| Тып інтэрфейсу: | I2C |

| Адчувальны да вільгаці: | так |

| Тып прадукту: | DSP - працэсары і кантролеры лічбавых сігналаў |

| Завадская колькасць упакоўкі: | 160 |

| Падкатэгорыя: | Убудаваныя працэсары і кантролеры |

| Напружанне сілкавання - макс.: | 1,65 В |

| Напружанне сілкавання - Мін.: | 1,55 В |

| Вартавыя таймеры: | Вартавы таймер |

♠ Працэсар лічбавых сігналаў TMS320VC5509A з фіксаванай кропкай

Працэсар лічбавых сігналаў з фіксаванай кропкай (DSP) TMS320VC5509A заснаваны на працэсарным ядры працэсара пакалення TMS320C55x DSP.Архітэктура C55x™ DSP забяспечвае высокую прадукцыйнасць і нізкую магутнасць за кошт павелічэння паралелізму і поўнай канцэнтрацыі на зніжэнні рассейванай магутнасці.Цэнтральны працэсар падтрымлівае ўнутраную структуру шыны, якая складаецца з адной праграмнай шыны, трох шын чытання даных, дзвюх шын запісу даных і дадатковых шын, прызначаных для дзейнасці перыферыйных прылад і DMA.Гэтыя шыны забяспечваюць магчымасць выканання да трох чытанняў дадзеных і двух запісаў дадзеных за адзін цыкл.Паралельна кантролер DMA можа выконваць да двух перадач даных за цыкл незалежна ад актыўнасці працэсара.

ЦП C55x забяспечвае два блокі множання-назапашвання (MAC), кожны з якіх здольны множыць 17 х 17 біт за адзін цыкл.Цэнтральны 40-бітны арыфметычна-лагічны блок (ALU) падтрымліваецца дадатковым 16-бітным ALU.Выкарыстанне ALU знаходзіцца пад кантролем набору інструкцый, што дае магчымасць аптымізаваць паралельную дзейнасць і энергаспажыванне.Гэтыя рэсурсы кіруюцца ў адрасным блоку (AU) і блоку даных (DU) працэсара C55x.

Пакаленне C55x DSP падтрымлівае набор інструкцый з пераменнай шырынёй байтаў для павышэння шчыльнасці кода.Блок інструкцый (IU) выконвае выбарку 32-бітнай праграмы з унутранай або знешняй памяці і ставіць у чаргу інструкцыі для праграмнага блока (PU).Праграмны блок дэкадуе інструкцыі, накіроўвае задачы на рэсурсы AU і DU і кіруе цалкам абароненым канвеерам.Магчымасць прагназавання разгалінавання дазваляе пазбегнуць прамывання канвеера пры выкананні ўмоўных каманд.

Функцыі ўводу і вываду агульнага прызначэння і 10-бітны A/D забяспечваюць дастатковую колькасць кантактаў для стану, перапыненняў і бітавага ўводу/вываду для ВК-дысплеяў, клавіятур і медыя-інтэрфейсаў.Паралельны інтэрфейс працуе ў двух рэжымах: як падпарадкаваны мікракантролер з дапамогай порта HPI або як паралельны медыя-інтэрфейс з выкарыстаннем асінхроннага EMIF.Паслядоўны носьбіт падтрымліваецца двума перыферыйнымі прыладамі MultiMedia Card/Secure Digital (MMC/SD) і трыма McBSP.

Набор перыферыйных прылад 5509A уключае інтэрфейс знешняй памяці (EMIF), які забяспечвае бесклейкі доступ да асінхроннай памяці, такой як EPROM і SRAM, а таксама да высакахуткаснай памяці высокай шчыльнасці, такой як сінхронная DRAM.Дадатковыя перыферыйныя прылады ўключаюць універсальную паслядоўную шыну (USB), гадзіннік рэальнага часу, вартавы таймер, I2C мульты-галоўны і падпарадкаваны інтэрфейс.Тры поўнадуплексных шматканальных паслядоўных партоў з буферызацыяй (McBSP) забяспечваюць бесклейкі інтэрфейс для розных паслядоўных прылад прамысловага стандарту і шматканальную сувязь з да 128 асобна ўключанымі каналамі.Палепшаны інтэрфейс хост-порта (HPI) - гэта 16-бітны паралельны інтэрфейс, які выкарыстоўваецца для забеспячэння доступу хост-працэсара да 32 Кбайт унутранай памяці на 5509A.HPI можа быць сканфігураваны як у мультыплексаваным, так і ў немультыплексаваным рэжыме, каб забяспечыць бесклейкі інтэрфейс для шырокага спектру хост-працэсараў.Кантролер DMA забяспечвае перамяшчэнне дадзеных для шасці незалежных кантэкстаў канала без умяшання працэсара, забяспечваючы прапускную здольнасць DMA да двух 16-бітных слоў за цыкл.Таксама ўключаны два таймера агульнага прызначэння, да васьмі спецыяльных кантактаў уводу-вываду агульнага прызначэння (GPIO) і генерацыя тактавых сігналаў з лічбавай фазавай аўтападстройкай частот (DPLL).

5509A падтрымліваецца адзначанай узнагародамі eXpressDSP™, інтэграваным асяроддзем распрацоўкі (IDE) Code Composer Studio™, DSP/BIOS™, стандартам алгарытмаў Texas Instruments і найбуйнейшай у галіны сеткай іншых вытворцаў.IDE Code Composer Studio змяшчае інструменты генерацыі кода, уключаючы кампілятар C і Visual Linker, сімулятар, драйверы прылад эмуляцыі RTDX™, XDS510™ і модулі ацэнкі.5509A таксама падтрымліваецца бібліятэкай C55x DSP, якая змяшчае больш за 50 асноўных праграмных ядраў (фільтры FIR, фільтры IIR, FFT і розныя матэматычныя функцыі), а таксама бібліятэкі падтрымкі мікрасхем і плат.

Ядро TMS320C55x DSP было створана з адкрытай архітэктурай, якая дазваляе дадаваць апаратнае забеспячэнне для канкрэтных прыкладанняў для павышэння прадукцыйнасці на пэўных алгарытмах.Апаратныя пашырэнні на 5509A забяспечваюць ідэальны баланс паміж прадукцыйнасцю фіксаванай функцыі і праграмуемай гнуткасцю, забяспечваючы пры гэтым нізкае энергаспажыванне і кошт, якія традыцыйна было цяжка знайсці на рынку відэапрацэсараў.Пашырэнні дазваляюць 5509A забяспечваць выключную прадукцыйнасць відэакодэка з больш чым паловай прапускной здольнасці, даступнай для выканання дадатковых функцый, такіх як пераўтварэнне каляровай прасторы, аперацыі карыстальніцкага інтэрфейсу, бяспека, TCP/IP, распазнаванне голасу і пераўтварэнне тэксту ў маўленне.У выніку адзін DSP 5509A можа забяспечваць большасць партатыўных праграм лічбавага відэа з запасам апрацоўкі.Для атрымання дадатковай інфармацыі гл. Даведнік праграміста TMS320C55x Hardware Extensions for Image/Video Applications (літаратурны нумар SPRU098).Для атрымання дадатковай інфармацыі аб выкарыстанні бібліятэкі апрацоўкі малюнкаў DSP глядзіце Даведнік праграміста бібліятэкі апрацоўкі малюнкаў/відэа TMS320C55x (нумар літаратуры SPRU037).

• Высокапрадукцыйны лічбавы сігнальны працэсар з фіксаванай кропкай TMS320C55x™ з нізкім энергаспажываннем

− 9,26-, 6,95-, 5-нс Час цыклу інструкцыі

− 108-, 144-, 200-МГц тактавая частата

− Адна/дзве інструкцыі, якія выконваюцца за цыкл

− Двайныя множнікі [Да 400 мільёнаў множных назапашванняў у секунду (MMACS)]

− Два арыфметычных/лагічных блока (ALU)

− Тры ўнутраныя шыны для чытання дадзеных/аперанда і дзве ўнутраныя шыны для запісу даных/аперанда

• 128K x 16-разрадная аператыўная памяць у чыпе, якая складаецца з:

− 64K байт аператыўнай памяці з падвойным доступам (DARAM) 8 блокаў 4K × 16-біт

− 192K байт аператыўнай памяці з адным доступам (SARAM) 24 блокі 4K × 16-біт

• 64 КБ ПЗУ з адным станам чакання (32 К × 16 біт)

• 8M × 16-бітная максімальная адрасная прастора вонкавай памяці (сінхронная DRAM)

• 16-бітная знешняя паралельная шына памяці з падтрымкай:

− Інтэрфейс знешняй памяці (EMIF) з магчымасцямі GPIO і бесклеевым інтэрфейсам для:

− Асінхронная статычная аператыўная памяць (SRAM)

− Асінхроннае EPROM

− Сінхронная DRAM (SDRAM)

− 16-разрадны пашыраны інтэрфейс хост-порта (EHPI) з магчымасцямі GPIO

• Праграмуемае кіраванне нізкім энергаспажываннем шасці функцыянальных даменаў прылады

• Логіка эмуляцыі на аснове сканавання на чыпе

• Перыферыйныя прылады на чыпе

− Два 20-бітных таймера

− Вартавы таймер

− Шасціканальны кантролер прамога доступу да памяці (DMA).

− Тры паслядоўныя парты, якія падтрымліваюць камбінацыю:

− Да 3 шматканальных буферызаваных паслядоўных партоў (McBSP)

− Да 2 інтэрфейсаў MultiMedia/Secure Digital Card

− Праграмуемы тактавы генератар з фазавай аўтападстройкай частот

− Сем (LQFP) або восем (BGA) кантактаў уводу-вываду агульнага прызначэння (GPIO) і выхадны кантакт агульнага прызначэння (XF)

− Поўнахуткасны (12 Мбіт/с) падпарадкаваны порт USB з падтрымкай масавых, перапыненых і ізахронных перадач

− Міжінтэгральная схема (I2C) з некалькімі галоўнымі і падпарадкаванымі інтэрфейсамі

−Гадзіннік рэальнага часу (RTC) з крыштальным уваходам, асобным даменам гадзінніка, асобным крыніцай харчавання

− 4-канальны (BGA) або 2-канальны (LQFP) 10-бітны А/Ц паслядоўнага набліжэння

• Логіка памежнага сканавання IEEE Std 1149.1† (JTAG).

• пакеты:

− 144-канальны нізкапрофільны чатырохканальны пакет (LQFP) (суфікс PGE)

− 179-кантактны MicroStar BGA™ (шарыкавы масіў) (суфікс GHH)

− 179-кантактны бессвінцовы MicroStar BGA™ (шарыкавы масіў) (суфікс ZHH)

• Ядро 1,2 В (108 МГц), 2,7 В – 3,6-VI/Os

• Ядро 1,35-В (144 МГц), 2,7-В – 3,6-VI/Os

• Ядро 1,6-В (200 МГц), 2,7-В – 3,6-VI/Os

• Гібрыдная, электрычная і сілавая сістэма (EV/HEV)

- Сістэма кіравання батарэяй (BMS)

- Бартавая зарадная прылада

– Цягавы інвертар

– DC/DC пераўтваральнік

- Стартар/генератар